ApplicationsJanuary 9, 2020

Enabling robust condition-based monitoring for Industry 4.0

To meet the demands of Industry 4.0, condition-based monitoring (CbM) of robotics and rotating machines, such as turbines, fans, pumps, and motors, offers a method for record real-time data related to the health and performance of machines to enable targeted predictive maintenance, as well as optimized control.

Government initiatives, such as Germany’s Industrie 4.0 and China’s Made in China 2025, are accelerating the trend towards ubiquitous networked automation in manufacturing. In addition, automation is being enhanced by smart sensor systems with more data available to monitor and control production processes.

In particular, Made in China 2025 aims to rapidly develop high tech industries, including electric vehicles, next-generation information technology (IT) and telecommunications, and advanced robotics and artificial intelligence. With more advanced systems there is a need for more advanced ways to ensure system reliability.

Condition-based monitoring (CbM) of robotics and rotating machines, such as turbines, fans, pumps, and motors, records real-time data related to the health and performance of the machine to enable targeted predictive maintenance, as well as optimized control. Targeted predictive maintenance, early in the machine life cycle, reduces the risk of production downtime resulting in increased reliability, significant cost savings, and increased productivity on the factory floor.

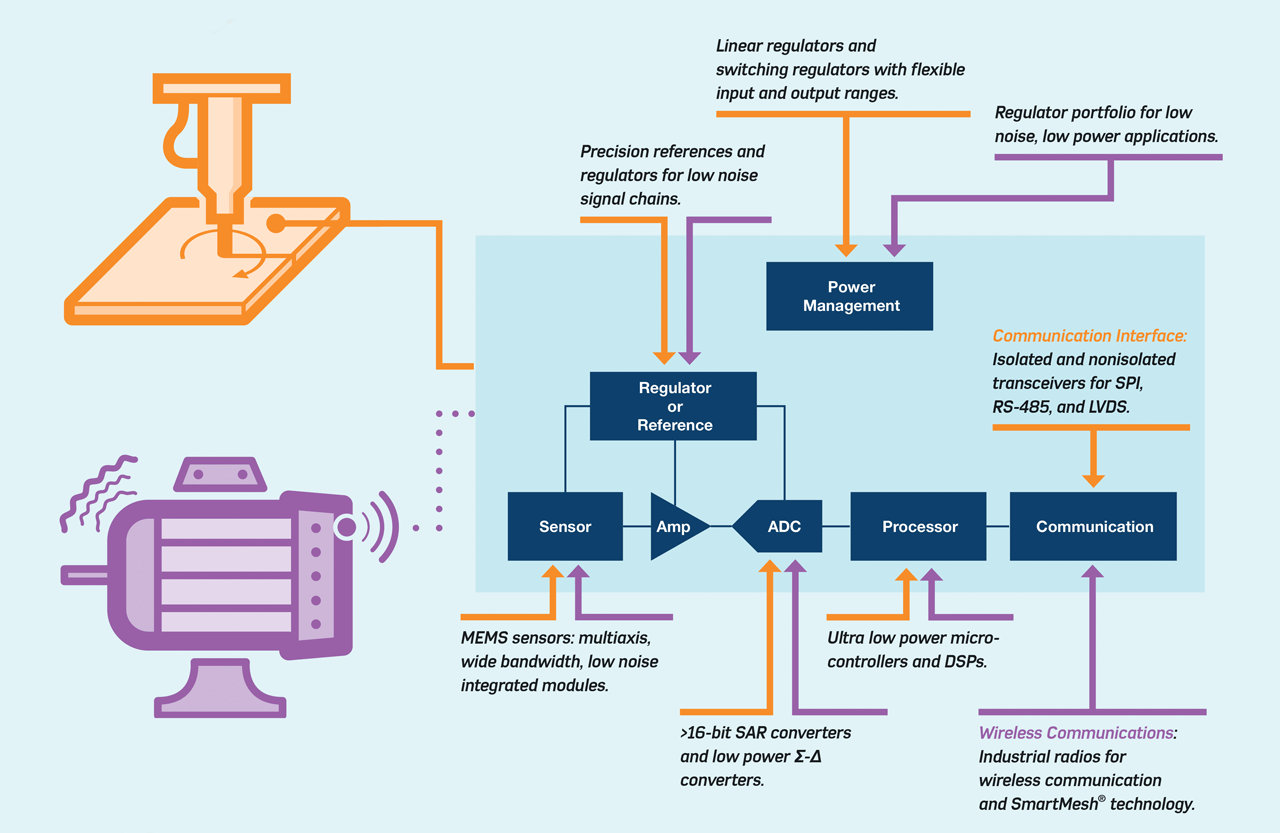

Wireless Signal Chain Example for Motor Monitoring: Monitoring of factory equipment in difficult to access locations requires wireless solutions that eliminate the need for extra cables while providing critical information over a robust wireless link. Low power components coupled with high performance sensors in compact form factors create new condition monitoring opportunities for a wide variety of factory applications, while minimizing the complexities of integrating into existing and new factory equipment.

Condition-based monitoring

Condition-based monitoring of industrial machines can utilize a range of sensor data, such as electrical measurements, vibration, temperature, oil quality, acoustic, and process measurements such as flow and pressure. However, vibration measurement is the most common by far, as it can provide the most reliable indication of mechanical issues such as imbalance and bearing failure. This article focuses on the use of vibration sensing, but the methodology is equally applicable to data from other sensors.

The transmission means of the sensor data from the sensing node to the main controller or the cloud is highly dependent on applications. In many applications, some local data processing is implemented at the edge node, with summary data being subsequently transmitted wirelessly to a network gateway, or directly via a cellular link to the cloud or analytics server. In these situations, the amounts of data transmitted are typically rather low, and there is often a requirement for low power as the edge node can be battery powered.

In other applications, raw sensor data transmission is required. For example, aligning and fusing data from multiple sensors may be required prior to analysis. Raw data transmission is also required in applications where data is utilized for real-time control. In these applications, a wired interface is a more likely solution for data transmission.

CbM of industrial applications can leverage Analog Devices’ optimized signal chain of Micro-ElectroMechanical Systems (MEMS) accelerometers, low power microcontrollers, and wired iCoupler isolated interfaces to extract, condition, and reliably communicate machine health data from a remote CbM slave back to a master controller for analysis. Over time, machine health data can be used to create software-based models to determine changes in machine behavior and proactively maintain machine health. In some applications, such as CNC machines, the data can also be used to optimize the performance of the system in real time.

The challenges with implementing a wired CbM interface include EMC robustness when operating over long cables, data integrity with transmitting at a high baud rate (for real-time CbM data streaming), and communication physical layer/protocol mismatches. Analog Devices’ signal chain and system-level expertise provides several possible options to implement a wired CbM interface.

RS-485/RS-422 design solutions

Wired interface solutions reduce customer design cycle and test time, and enable faster time to market for industrial CbM solutions. Several aspects for discussion include selecting a suitable MEMS accelerometer and physical layer, as well as EMC performance and power design. Potential design solutions include performance trade-offs. This article focuses on design considerations for SPI to RS-485/RS-422 design solutions.

Common challenges in implementing a wired physical layer interface for MEMS include managing EMC robustness and data integrity.

However, when extending a clock synchronized interface such as SPI over long RS-485/RS-422 cables, along with combining power and data on the same twisted pair wires (phantom power), several additional challenges are presented. This article discusses the following key considerations and provides recommendations for designing the physical layer interface:

- Managing system time synchronization

- Data rate vs. cable length recommendations

- Filter design and simulation for shared power and data architectures

- Passive component performance trade-offs for phantom power implementation

- Component selection and system design window

- Experimental measurements

Time Synchronization/Cable Length

When designing an SPI to RS-485/RS-422 link, the cable and components affect system clock and data synchronization. Over a long cable run, the SCLK signal will incur a propagation delay through the cable, approximately 400 ns to 500 ns for a 100 m cable. For a MOSI data transfer, the MOSI and SCLK are equally delayed by the cable.

However, data sent from the slave MISO to the master will be out of sync with the SCLK by twice the cable propagation delay. The maximum possible SPI SCLK is set by the system propagation delay, which includes cable propagation delay as well as master and slave component propagation delays.

System propagation delay can lead to inaccurate SPI MISO sampling at the SPI master. For a system without an RS-485/RS-422 cable, MISO data and SPI SCLK will be synchronized with little or no delay. For a system with a cable, MISO data at the SPI slave is out of sync with SPI SCLK by one system propagation delay.

MISO data arrives back at the master out of sync by two system propagation delays. As data is shifted right due to cable and component propagation delays, inaccurate data sampling occurs.

To prevent inaccurate MISO sampling, one may reduce the cable length, lower the SPI SCLK, or implement an SPI SCLK compensation scheme (clock phase shift) in the master controller. Theoretically, the system propagation delay should be less than 50% of the SCLK clock period for error free communication, and in practice a limit of system delay of 40% SCLK can be used as a general rule.

An SPI SCLK vs. cable length guideline for the two SPI to RS-485/RS-422 designs is needed. The non-isolated design uses Analog Devices’ high speed EMC robust and small form factor RS-485/RS-422 devices (ADM3066E and ADM4168E). The isolated design also includes Analog Devices’ iCoupler signal and power isolated ADuM5401 device, which provides additional EMC robustness and noise immunity for SPI to RS-485/RS-422 links. This design adds additional system propagation delay, which limits operation at higher SPI SCLK rates.

Over longer cable runs (greater than 30 m) adding isolation is strongly recommended to help mitigate against ground loops and EMC events such as electrostatic discharge (ESD), electrical fast transients (EFT), and high voltage surges coupling to the data transmission cabling. When cable lengths extend to 30 m or greater, the SPI SCLK vs. cable length performance of the isolated vs. non-isolated design is similar.

Background

Phantom power combines power and data on a single twisted pair—enabling a one-cable solution between master and slave devices. Combining both data and power on a single cable enables a one-connector solution at space constrained edge sensor nodes.

Power and data are distributed on a single twisted pair using an inductor capacitor network integrated into the design. High frequency data is coupled to the data lines through series capacitors, which also protect the RS-485/RS-422 transceiver from dc bus voltages.

High-Pass Filter

For the purposes of this article, it is assumed that the phantom power inductor-capacitor network is added to two wires, which route the RS-485/RS-422 conversion of the SPI MISO signal. The filter circuit is high pass, and requires that the data signals being transmitted do not have content at dc or at very low frequencies.

Using a second-order high-pass filter circuit, the voltage output at the transmitting RS-485/RS-422 device is noted as VTX, with R1 15 Ω output impedance. The R2 30 kΩ is a standard input impedance for the receiving RS-485/RS-422 device. Inductor (L) and capacitor (C) values can be selected to suit the desired system data rate.

When choosing the inductor (L) and capacitor (C) values, the maximum RS-485/RS-422 bus voltage droop and droop time need to be considered. Standards exist, such as single twisted-pair Ethernet, which specify the maximum allowable voltage droop and droop time.

For some systems the maximum permissible voltage droop and droop time may be larger, limited by the signal polarity crossover point. The voltage droop and droop time can be used paired with a simulation to determine the system high pass frequency.

When adding phantom power to an SPI to RS-485/RS-422 communication system, it is clear that the minimum possible SPI SCLK rate will be limited by the phantom power filter components.

To achieve reliable communication without bit errors, one need consider the minimum SPI SCLK in a worst-case scenario—for example, where all SPI MISO sampled bits are logic high.

If all sampled MISO bits are logic high, then this results in a bit rate lower than the system SPI SCLK. For example, if the SPI SCLK is 2 MHz and all 16 bits are logic high, then the phantom power LC filter network will see an equivalent SPI MISO bit rate of 125 kHz.

As noted in the section “Time Synchronization and Cable Length,” longer cable lengths require lower SPI SCLK rates. However, phantom power limits the lowest possible SPI SCLK rate. Balancing these opposing requirements involves careful selection and characterization of passive filter components, particularly inductors.

Passive Component Selection

When selecting a suitable power inductor, a number of parameters need to be considered, including sufficient inductance, rated/saturation current, self-resonant frequency (SRF), low dc resistance (DCR), and package size.

The rated current needs to meet or exceed the total current requirements for the remotely powered MEMS sensor node, and the rated saturation current needs to be much larger.

The inductor will not present high impedance to ac data above its quoted SRF, and at a certain point will begin to have a capacitive impedance characteristic. The chosen inductor SRF will limit the maximum SPI SCLK that can be used on the SPI to RS-485/RS-422 physical layer.

When operating over long cables the inductor SRF may not be reached; for example, reaching SPI SCLK rates of 11 MHz (part number 744043101’s SRF) over 10 m of cable may not be possible. In other cases, when operating over long cables the inductor SRF may be reached for lower SPI SCLK rates (2.4 MHz, 1.2 MHz). As noted previously, when used in a phantom power filter network, an inductor will also limit the lowest possible SCLK rate.

The constraints in choosing a suitable dc voltage blocking capacitor are limited to the transient overvoltage rating and dc voltage rating of the system.

The dc voltage rating needs to exceed the maximum bus voltage bias. During a cable or connector short, the inductor currents will become imbalanced and will be dissipated by termination resistances. DC blocking capacitors need to be rated for peak transient voltages in the event of a short. For example, in lower power systems, with inductor saturation currents of about 1 A, the corresponding dc blocking capacitor should be rated to at least 50 V dc.

Design and component selection

When extending a clock synchronized interface such as SPI over long RS-485/RS-422 cables, along with combining power and data on the same twisted pair wires (phantom power), the minimum possible SPI SCLK is set by the phantom power filter components, which high-pass filter data on the SPI data line. The maximum SPI SCLK is set by either the phantom power inductor self-resonant frequency (SRF) or the system propagation delay (whichever SPI SCLK is lower in value).

Experimental Setup

A CbM evaluation system (Pioneer 1) uses SPI to RS-485/RS-422 design solutions. Pioneer 1 also includes the ADcmXL3021 wide bandwidth, low noise, triaxial MEMS accelerometer, which combines high performance with a variety of signal processing to simplify the development of smart sensor nodes in CbM systems.

The SPI to RS-485/RS-422 slave extends the ADcmXL3021 SPI output over 10 m back to the master controller for vibration data analysis in the system. The SPI to RS-485 designs use phantom power 100 µH inductors and 3.3 µF capacitors to minimize the size of the slave interface solutions, which measure 26 mm × 28 mm (excluding interface connector).

Voltages measured at the SPI master and slave, and on the RS-485/RS-422 differential voltage bus were measured using a sample application setup.

The analog signals 1 and 2 are the differential bus voltage representation of the MISO signal, as measured at the SPI slave output. The digital signal 4 shows the MISO sampled at the master controller. The MISO signal at the SPI master matches the polarity and phase of the MISO at the SPI slave, with little propagation delay.

Analog Devices has developed the Pioneer 1 wired system evaluation solution to support the ADcmXL3021 triaxial MEMS accelerometer. The Pioneer 1 evaluation kits can also support MEMS devices with the help of the expansion board described in the wiki guide.